IngOehman skrev:...

Nu finns ju väldigt stora och snabba minnen till bra priser, men om man skulle göra en idealisk sinc med upplösning som tangerar blygsamma 16 bitars upplösning trots grov trunkering av sincen, så talar vi om delayer om 20 000 samples, alltså runt en halv sekund. Vill vi närma oss 20 bitar så blir det 300 000 samples... Det är en klart märkbar delay, även när man bara spelar CD, även om man självklart kan hävda att det går att trycka på play 8 sekunder tidigare.

Men om man vill ha 24 bitars upplösning då, även i det korta perspektivet? Det blir typ 5 000 000 samples delay, alltså runt två minuter i fördröjning...

PS. Resonemanget härovan utgår ifrån en samplingsfrekvens på lite mera än 2 x 20 000 Hz.

Vh, iö

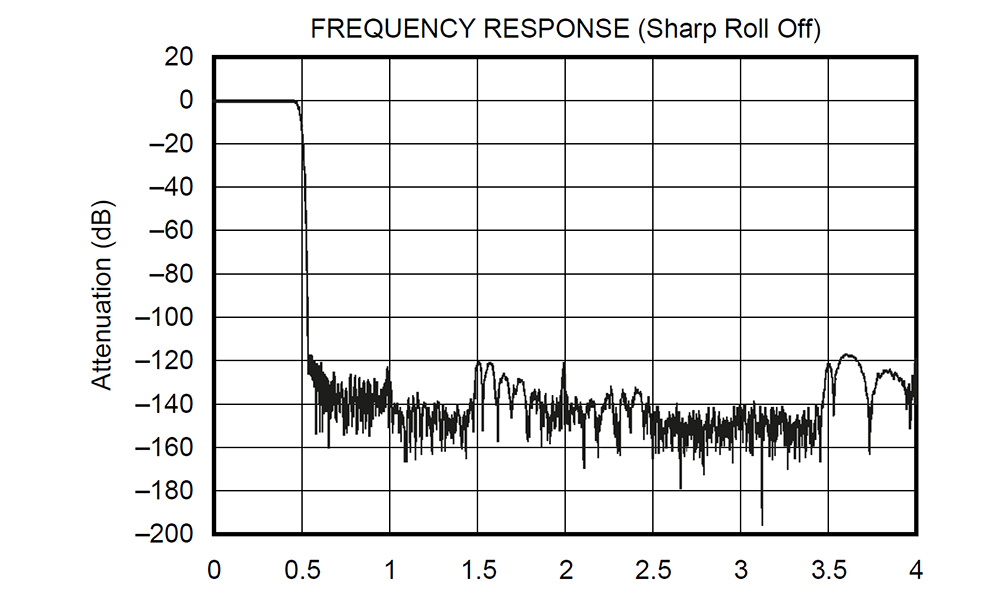

Ingvar, det finns helt andra sätt att göra detta på som gör att man exempelvis får 256 000 tappar d v s samples delay med totalt sett inte mer än 45 ms fördröjning. Det sker då upsampling i de olika stegen. Då har man dessutom alla beräkningar i 36 bitar vilket blir ett krav om man skall beräkna korrekta resultat med lågt digitalt brus. Dessutom kan man använda ett betydligt snyggare tidsfönster än rektangulärt d v s trunkering.

I den DAC som jag nu utvecklar med lilltroll så kan vi få 5 000 000 samples delay d v s taps i de digitala filtren där tidsfördröjningen totalt blir 55,36 ms d v s lite drygt 55 ms. Det är då förenat med upsampling vilket är en självklarhet om man skall införa digitala filter. Då kan man räkna baklänges och få fram vilken upsampling vi har.

Då man väljer antalet taps i varje upsamplingssteg så bör man veta att efter ett visst antal taps så är nivån på sincen lägre än exempelvis LSB på 16 bitar och antingen har man ett tidsfönster som anpassas eller så får man räkna med exempelvis 24 bitar eller mer. Annars blir ett stort antal taps helt meningslöst. Jag kan redan nu säga att det faktiskt finns de omvandlare där efter ett visst antal taps multiplikationen d v s resultatet alltid blir noll eftersom upplösningen i processen är för låg, men det kan ju vara kul att skryta med en massa taps. Jag och lilltroll väljer en annan väg.

Vi har just nu simulerat hur de olika stegen ser ut med 36 bitar i varje steg och det verkar räcka och bli över. Dagens kretsar är så pass snabba att man kan få otrolig beräkningskapacitet om man utnyttjar kretsarna intill max.

Efter diskussionerna i den här tråden har jag beslutat att se vad vi kan uppnå om vi utnyttjar befintlig FPGA till 99 %. Hittills har vi utnyttjat 17 % vilket innebär att befintlig FPGA sover i 83 %

Jag har bestämt att den skall f-n upp och jobba i sitt anletes svett, FPGAn alltså.

Det är bara lite annorlunda mjukvara som skall till. Det arbetet blir kanske klart i nästa vecka.

Med vänlig hälsning

Peter

VD Bremen Production AB + Ortho-Reality AB; Grundare av Ljudbutiken AB; Fd import av hifi; Konstruktör av LICENCE No1 D/A, Bremen No1 D/A, Forsell D/A, SMS FrameSound, Bremen 3D8 m.fl.